# **Application Note AN-98 LinkSwitch-TNZ** Family

Buck and Buck-Boost Design Guide

#### Introduction

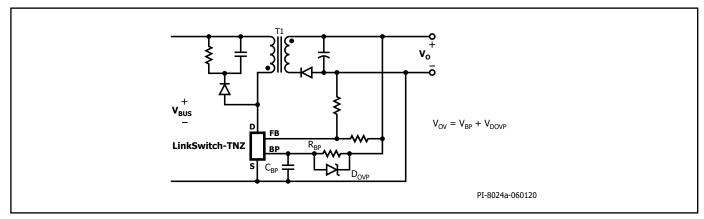

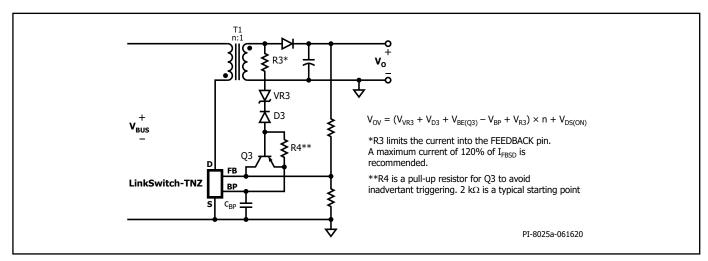

The LinkSwitch<sup>™</sup>-TNZ family of ICs combine power conversion with lossless generation of an AC zero crossing signal. This signal is typically used for system clock and timing functions. Designs using the highly integrated LinkSwitch-TNZ ICs reduce component count more than 40% compared to discrete solutions. As well as enabling efficiency greater than 80% in low power flyback designs, the very low consumption at light load enabled by ON/OFF control allows for more functions (display, wireless connectivity, sensors etc.) to be active during system standby. The LinkSwitch-TNZ family is highly flexible, supporting buck, buck-boost and flyback converter topologies.

Each device incorporates a 725 V power MOSFET, driver, oscillator, a high-voltage switched current source for self-biasing, frequency jittering, fast (cycle-by-cycle) current limit and protection into a monolithic IC.

LinkSwitch-TNZ ICs consume less than 100  $\mu A$  in no-load operation resulting in power supply designs that can meet no-load and standby regulations worldwide. MOSFET current limit thresholds can be selected through the BYPASS pin capacitor value. Choosing the high current limit provides maximum continuous output current while selecting the low current limit permits the use of small surface mount inductors. The comprehensive suite of protection features means that LinkSwitch-TNZ-based power supplies protect both the power supply itself and the system against input and output overvoltage and undervoltage faults. The LinkSwitch-TNZ ICs also protect against device over-temperature faults, lost regulation, and power supply output overload or short-circuit faults.

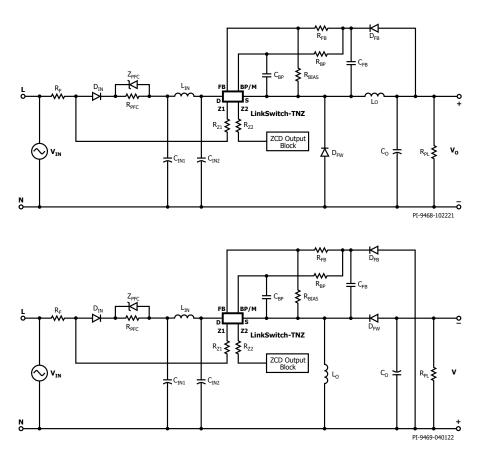

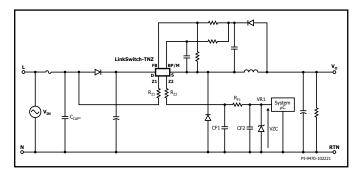

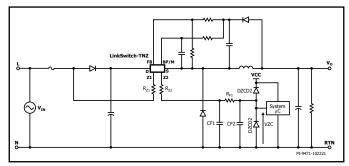

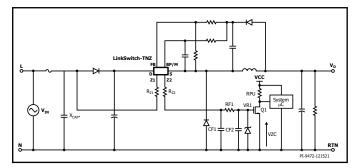

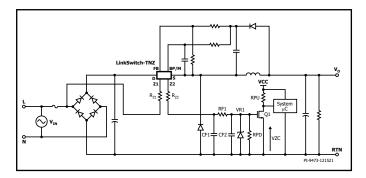

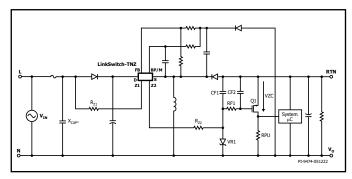

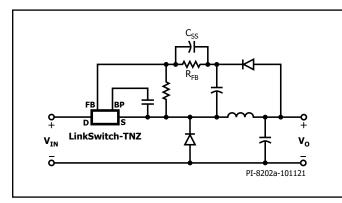

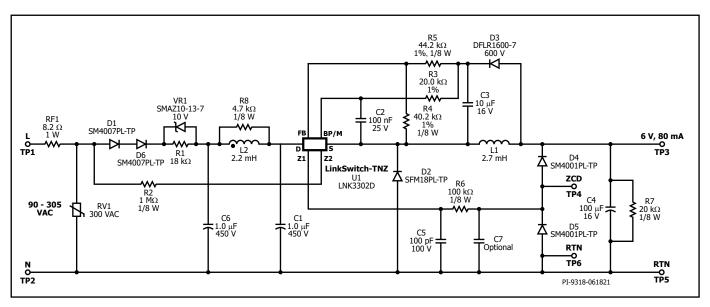

Figure 1. Basic Configuration Using LinkSwitch-TNZ in a Buck Converter, 1(a) and Buck-Boost Converter, 1(b).

#### Scope

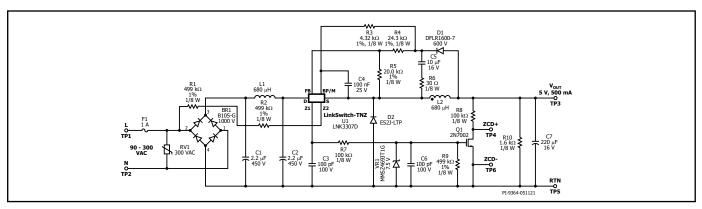

This application note provides information for designing a nonisolated power supply using the LinkSwitch-TNZ family of devices. This document describes the design procedure for buck and buck-boost converters. The objective of this document is to provide power supply engineers with quidelines in order to enable them to quickly build efficient buck or buck-boost converter based power supplies using low-cost off-the- shelf inductors. Complete design equations are provided for the selection of the converter's key components. Since the power MOSFET and controller are integrated into a single IC, the design process is greatly simplified, the circuit configuration has few parts and no transformer is required. Therefore a quick start section is provided that allows easy selection of components for typical output voltages and currents. To simplify the task this application note refers directly to the PIXIs design spreadsheet that is part of the PI Expert™ design software suite (go to power.com for a free download of the design software or to use the web version of PI Expert). The basic schematic for LinkSwitch-TNZ power supplies is shown in Figure 1, which also serves as the reference circuit for component identifications throughout this application note.

In addition to this application note, the reader may also find the LinkSwitch-TNZ Reference Design Kit (RDK) containing an engineering prototype board and engineering report useful as an example of a working power supply. Further details on downloading PI Expert, obtaining a RDK and updates to this document can be found at www. power.com.

#### **Quick Start**

Readers familiar with power supply design and wanting to start immediately can use the following information to select the components for a new design, using Figure 1 and Tables 1 and 2 as references.

- 1. For AC input designs select the input stage (Table 9).

- Select the topology (Tables 1 and 2). If better than ±5% output regulation is required, then use of optocoupler feedback and not with suitable reference such as a TL431 or a precision Zener is required.

- Select the LinkSwitch-TNZ device, L<sub>o</sub>, R<sub>FB</sub> or V<sub>z</sub>, R<sub>BIAS</sub>, C<sub>FB</sub>, R<sub>z</sub> and the reverse recovery time for D<sub>FW</sub> (Table 4: Buck, Table 5: Buck-Boost).

- 4. Select freewheeling diode to meet t<sub>pp</sub> determined in Step 3 (table 3).

- 5. For direct feedback designs, if the minimum load <3 mA then calculate  $\rm R_{\rm pL} = \rm V_{\rm o}/3$  mA.

- 6. Select  $C_0$  as 100  $\mu$ F, 1.25  $\times$   $V_0$ , low ESR type.

- 7. Construct prototype and verify design.

#### Notes:

- 1. Directly sensed feedback typically achieves overall regulation tolerance of ±5% with 3 mA pre-load for 12 V design.

- 2. To ensure output regulation, a pre-load may be required to maintain a minimum load current of 3 mA (buck and buck-boost only).

- 3. Boost topology (step-up) is also possible but not shown.

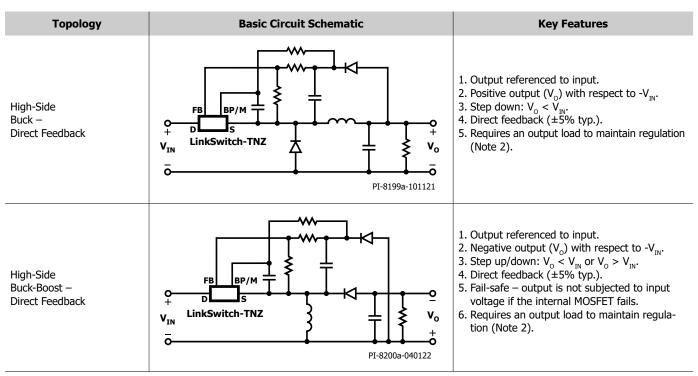

Table 1. LinkSwitch-TNZ Circuit Configurations using Directly Sensed Feedback.

| Topology                                    | Basic Circuit Schematic                         | Key Features                                                                                                                                                                                                                                                                            |

|---------------------------------------------|-------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| High-Side<br>Buck –<br>Optocoupler Feedback | LinkSwitch-TNZ  V <sub>IN</sub> PI-8199a-112221 | <ol> <li>Output referenced to input.</li> <li>Positive output (V<sub>o</sub>) with respect to -V<sub>IN</sub>.</li> <li>Step down: V<sub>o</sub> &lt; V<sub>IN</sub>.</li> <li>Direct feedback (±5% typ.).</li> <li>Requires an output load to maintain regulation (Note 2).</li> </ol> |

#### Notes:

- 1. Regulation of optocoupler feedback only limited by accuracy of reference (Zener or IC).

- 2. Optocoupler does not need to be safety approved.

- 3. The current for the reference voltage acts as a pre-load. The value of RZ is determined by Zener test current or reference IC bias current, typically 470  $\Omega$  to 2 k $\Omega$ , 1/8 W, 5%.

- 4. Boost topology (step-up) is also possible but not shown.

- 5. Optocoupler feedback provides lowest no-load consumption.

Table 2. LinkSwitch-TNZ Circuit Configurations using Optocoupler Feedback.

| Part Number | V <sub>RRM</sub> | I <sub>F</sub> | t <sub>rr</sub> | Package | Manufacturer        |  |

|-------------|------------------|----------------|-----------------|---------|---------------------|--|

| Part Number | (V)              | (A)            | (ns)            | Factage | Flandiacturei       |  |

| MUR160      | 600              | 1              | 50              | Leaded  | Vishay              |  |

| UF4005      | 600              | 1              | 75              | Leaded  | Vishay              |  |

| BYV26C      | 600              | 1              | 30              | Leaded  | Vishay/Philips      |  |

| FE1A        | 600              | 1              | 35              | Leaded  | Vishay              |  |

| STTA10 6    | 600              | 1              | 20              | Leaded  | ST Microelectronics |  |

| STTA10 6U   | 600              | 1              | 20              | SMD     | ST Microelectronics |  |

| US1J        | 600              | 1              | 75              | SMD     | Vishay              |  |

| SFM18PL     | 600              | 1              | 35              | SMD     | MCC                 |  |

Table 3. List of Ultrafast Diodes Suitable for use as the Freewheeling Diode.

| V <sub>оит</sub><br>(V) | Inductor  I <sub>OUT(MAX)</sub> (mA)  Typical Inductance (μH)  Inductor  Suggested LinkSwitch-TNZ Device |                     | tor               | Cummantad                |                                                    |                               |      |     |

|-------------------------|----------------------------------------------------------------------------------------------------------|---------------------|-------------------|--------------------------|----------------------------------------------------|-------------------------------|------|-----|

|                         |                                                                                                          |                     | Mode              | Diode<br>t <sub>rr</sub> | $R_{\rm FB}^*$ (k $\Omega$ )                       | V <sub>z</sub><br>(V)         |      |     |

|                         | ≤63<br>80                                                                                                | 2000<br>2400        | 88<br>96          | LNK33x2                  | MDCM<br>CCM                                        | ≤ 75 ns<br>≤ 35 ns            |      |     |

| _                       | 120<br>160                                                                                               | 910<br>1300         | 171<br>194        | LNK33x4                  | MDCM<br>CCM                                        | ≤ 75 ns<br>≤ 35 ns            | 2.40 | 2.0 |

| 5                       | 175<br>225                                                                                               | 620<br>1300         | 315<br>380        | LNK33x6                  | MDCM<br>CCM                                        | ≤ 75 ns<br>≤ 35 ns            | 3.48 | 3.9 |

|                         | 225<br>360                                                                                               | 470<br>820          | 564<br>642        | LNK33x7                  | MDCM<br>CCM                                        | ≤ 75 ns<br>≤ 35 ns            |      |     |

|                         | ≤63<br>80                                                                                                | 2000<br>2700        | 87<br>95          | LNK33x2                  | MDCM<br>CCM                                        | ≤ 75 ns<br>≤ 35 ns            |      |     |

| 12                      | 85<br>120<br>160                                                                                         | 910<br>1100<br>1800 | 143<br>166<br>189 | LNK33x4                  | MDCM<br>MDCM<br>CCM                                | ≤ 75 ns<br>≤ 75 ns<br>≤ 35 ns | 11.8 | 11  |

|                         | 175<br>225                                                                                               | 620<br>1500         | 315<br>378        | LNK33x6                  | MDCM<br>CCM                                        | ≤ 75 ns<br>≤ 35 ns            |      |     |

|                         | 225<br>360                                                                                               | 470<br>910          | 562<br>634        | LNK33x7                  | MDCM<br>CCM                                        | ≤ 75 ns<br>≤ 35 ns            |      |     |

|                         | ≤63<br>80                                                                                                | 2400<br>3300        | 85<br>93          | LNK33x2                  | MDCM<br>CCM                                        | ≤ 75 ns<br>≤ 35 ns            |      |     |

| 15                      | 70<br>120<br>160                                                                                         | 910<br>1300<br>2200 | 130<br>163<br>186 | LNK33x4                  | MDCM ≤ 75 ns<br>NK33x4 MDCM ≤ 75 ns<br>CCM ≤ 35 ns |                               | 15.4 | 13  |

| 15                      | 175<br>225                                                                                               | 680<br>1800         | 311<br>376        | LNK33x6                  | MDCM<br>CCM                                        | ≤ 75 ns<br>≤ 35 ns            | 15.1 | 15  |

|                         | 225<br>360                                                                                               | 470<br>1000         | 561<br>628        | LNK33x7                  | MDCM<br>CCM                                        | ≤ 75 ns<br>≤ 35 ns            |      |     |

|                         | ≤63<br>80                                                                                                | 3900<br>5100        | 81<br>90          | LNK33x2                  | MDCM<br>CCM                                        | ≤ 75 ns<br>≤ 35 ns            |      |     |

| 24                      | 50<br>120<br>160                                                                                         | 910<br>2000<br>3300 | 109<br>156<br>183 | LNK33x4                  | MDCM<br>MDCM<br>CCM                                | ≤ 75 ns<br>≤ 75 ns<br>≤ 35 ns | 25.5 | 22  |

|                         | 175<br>225                                                                                               | 1100<br>2700        | 296<br>373        | LNK33x6                  | MDCM<br>CCM                                        | ≤ 75 ns<br>≤ 35 ns            |      |     |

|                         | 225<br>360                                                                                               | 680<br>1600         | 524<br>609        | LNK33x7                  | MDCM<br>CCM                                        | ≤ 75 ns<br>≤ 35 ns            |      |     |

Other standard components  $R_{\text{BIAS}}$ : 2.49 kΩ, 1%, 1/8 W  $C_{\text{FB}}$ : 10 μF, 1.25 ×  $V_{\text{o}}$   $D_{\text{FB}}$ : 1N4005GP  $R_{\text{Z}}$ : 470 Ω to 2 kΩ, 1/8 W, 5%

Table 4. Components Quick Select for Buck Converters. \*Select nearest standard or combination of standard values.

|                         | Inductor                   |                               | Cummantad                |                                 |                     |                               |                          |     |

|-------------------------|----------------------------|-------------------------------|--------------------------|---------------------------------|---------------------|-------------------------------|--------------------------|-----|

| V <sub>out</sub><br>(V) | I <sub>OUT(MAX)</sub> (mA) | Typical<br>Inductance<br>(μΗ) | I <sub>RMS</sub><br>(mA) | Suggested LinkSwitch-TNZ Device | Mode                | Diode<br>t <sub>rr</sub>      | $R_{FB}^*$ (k $\Omega$ ) | (V) |

|                         | ≤60<br>80                  | 2000<br>2700                  | 88<br>96                 | LNK33x2                         | MDCM<br>CCM         | ≤ 75 ns<br>≤ 35 ns            |                          |     |

| _                       | 110<br>170                 | 910<br>1300                   | 165<br>196               | LNK33x4                         | MDCM<br>CCM         | ≤ 75 ns<br>≤ 35 ns            | 2.40                     |     |

| 5                       | 215<br>360                 | 620<br>1500                   | 311<br>390               | LNK33x6                         | MDCM<br>CCM         | ≤ 75 ns<br>≤ 35 ns            | 3.48                     | 3.9 |

|                         | 340<br>575                 | 470<br>910                    | 546<br>642               | LNK33x7                         | MDCM<br>CCM         | ≤ 75 ns<br>≤ 35 ns            |                          |     |

|                         | ≤55<br>80                  | 2200<br>3300                  | 82<br>96                 | LNK33x2                         | MDCM<br>CCM         | ≤ 75 ns<br>≤ 35 ns            |                          |     |

| 12                      | 85<br>105<br>170           | 910<br>1000<br>2700           | 146<br>160<br>201        | LNK33x4                         | MDCM<br>MDCM<br>CCM | ≤ 75 ns<br>≤ 75 ns<br>≤ 35 ns | 11.8                     | 11  |

|                         | 195<br>360                 | 620<br>3300                   | 299<br>417               | LNK33x6                         | MDCM<br>CCM         | ≤ 75 ns<br>≤ 35 ns            |                          |     |

|                         | 330<br>5780                | 470<br>1800                   | 543<br>664               | LNK33x7                         | MDCM<br>CCM         | ≤ 75 ns<br>≤ 35 ns            |                          |     |

|                         | ≤55<br>80                  | 2200<br>4300                  | 82<br>98                 | LNK33x2                         | MDCM<br>CCM         | ≤ 75 ns<br>≤ 35 ns            | _ 15.4                   | 13  |

| 15                      | 70<br>100<br>170           | 910<br>1100<br>3600           | 133<br>155<br>204        | LNK33x4                         | MDCM<br>MDCM<br>CCM | ≤ 75 ns<br>≤ 75 ns<br>≤ 35 ns |                          |     |

| 15                      | 195<br>335                 | 620<br>3000                   | 300<br>407               | LNK33x6                         | MDCM<br>CCM         | ≤ 75 ns<br>≤ 35 ns            |                          |     |

|                         | 315<br>550                 | 470<br>1800                   | 533<br>655               | LNK33x7                         | MDCM<br>CCM         | ≤ 75 ns<br>≤ 35 ns            |                          |     |

|                         | ≤50<br>80                  | 3300<br>9100                  | 77<br>105                | LNK33x2                         | MDCM<br>CCM         | ≤ 75 ns<br>≤ 35 ns            |                          |     |

| 24                      | 50<br>90<br>165            | 910<br>1600<br>6800           | 114<br>146<br>214        | LNK33x4                         | MDCM<br>MDCM<br>CCM | ≤ 75 ns<br>≤ 75 ns<br>≤ 35 ns | 25.5                     | 22  |

|                         | 170<br>300                 | 910<br>3600                   | 275<br>398               | LNK33x6                         | MDCM<br>CCM         | ≤ 75 ns<br>≤ 35 ns            |                          |     |

|                         | 825<br>510                 | 560<br>3000                   | 496<br>660               | LNK33x7                         | MDCM<br>CCM         | ≤ 75 ns<br>≤ 35 ns            |                          |     |

Other Standard Components: R<sub>BIAS</sub>: 2.49 k $\Omega$ , 1%, 1/8 W C<sub>FB</sub>: 10  $\mu$ F, 1.25 × V<sub>O</sub> D<sub>FB</sub>: 1N4005GP R<sub>2</sub>: 470  $\Omega$  to 2 k $\Omega$ , 1/8 W, 5%

Components Quick Select for Buck-Boost Converters. \*Select nearest standard or combination of standard values. The inductor values indicated in the table above are conservative estimates. In some designs it may be possible to reduce the inductance value further based on evaluation. Table 5.

#### **LinkSwitch-TNZ Circuit Design**

#### **LinkSwitch-TNZ Operation**

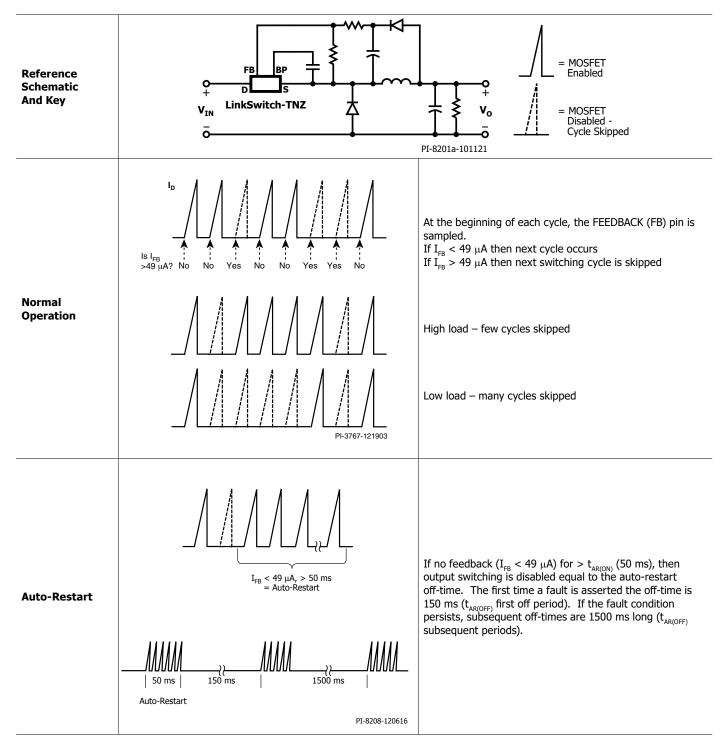

The basic circuit configuration for a buck converter using a LinkSwitch-TNZ IC is shown in Figure 1(a). To regulate the output, an ON/OFF control scheme is used as illustrated in Table 6. As the decision to switch is made on a cycle-by-cycle basis, the resultant power supply has extremely good transient response and removes

the need for control loop compensation components. If the output requests switching cycles (IFB < 49  $\mu A)$  continuously for longer then 50 ms then switching is inhabited and the circuit enters auto-restart mode. During auto-restart the duty cycle is reduced to prevent overheating of the power supply or damage to the board or load. If no feedback is received for 50 ms, then the supply enters auto-restart and switching is inhibited for a period of time to limit power dissipation.

Table 6. LinkSwitch-TNZ Operation.

To allow direct sensing of the output voltage without the need for a reference (Zener diode or reference IC), the FEEDBACK pin voltage is tightly toleranced over the entire operating temperature range. For example, this allows a 12 V design with an overall output tolerance of  $\pm 5\%$ . For higher performance, an optocoupler can be used with a reference as shown in Table 2. Since the optocoupler just provides level shifting, it does not need to be safety rated or approved. The use of an optocoupler also allows flexibility in the location of the device, for example it allows a buck converter configuration with the LinkSwitch-TNZ IC in the low-side return rail, reducing EMI as the SOURCE pins and connected components are no longer part of the switching node.

#### **Selecting the Topology**

If possible, use the buck topology. The buck topology maximizes the available output power from a given LinkSwitch-TNZ IC and inductor value. Also, the voltage stress on the power switch and freewheeling diode and the average current through the output inductor are slightly lower in the buck topology as compared to the buck-boost topology.

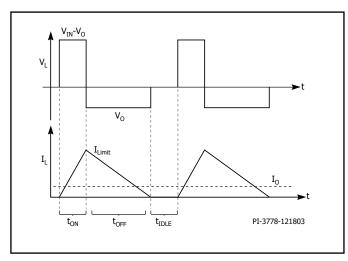

# **Selecting the Operating Mode – MDCM and CCM Operation**At the start of a design, select between mostly discontinuous conduction mode (MDCM) and continuous conduction mode (CCM) as this decides the selection of the LinkSwitch-TNZ device, freewheeling

diode and inductor. For maximum output current select CCM, for all other output components MDCM is recommended. Overall, select the operating mode and components to give the lowest overall solution cost. Table 7 summarizes the trade-offs between the two operating modes.

Additional differences between CCM and MDCM include better transient response for DCM and lower output ripple (for same capacitor ESR) for CCM. However these differences, at the low output currents of LinkSwitch-TNZ applications, are normally not significant.

The conduction mode CCM or MDCM of a buck or buck-boost converter primarily depends on input voltage, output voltage, output current and device current limit. The input voltage, output voltage and output current are fixed design parameters. The current limit for the LinkSwitch-TNZ is the design parameter that can be used to set the conduction mode, therefore the LinkSwitch-TNZ current limit is the only design parameter that sets the conduction mode.

The phrase "mostly discontinuous" is used with ON/OFF control, because while a few switching cycles may exhibit continuous inductor current flow, the majority of the switching cycles will be discontinuous. A design can be made fully discontinuous but that will limit the available output current, making the design less cost

#### effective.

| -                        | Comparison of CCM and MDCM Operating Modes                                                                                                                     |                                                                                                                                                                                                           |  |  |  |  |  |  |  |  |  |

|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|

| Operating Mode           | MDCM                                                                                                                                                           | ССМ                                                                                                                                                                                                       |  |  |  |  |  |  |  |  |  |

| Operating<br>Description | $I_{\text{L}}$ $t_{\text{ON}}$ $t_{\text{OFF}}$ $t_{\text{IDLE}}$ $p_{\text{I-3769-121803}}$ Inductor current falls to zero during $t_{\text{OFF}}$ borderline | $\begin{array}{c} I_L \\ \\ \hline \\ t_{\text{ON}} \\ \end{array}$ $\begin{array}{c} I_0 \\ \\ \hline \\ \text{PI-3770-121503} \\ \end{array}$ Current flows continuously in the inductor for the entire |  |  |  |  |  |  |  |  |  |

|                          | between MDCM and CCM when $t_{IDLE} = 0$ .                                                                                                                     | duration of a switching cycle.                                                                                                                                                                            |  |  |  |  |  |  |  |  |  |

| Inductor                 | Lower Cost<br>Lower value, smaller size.                                                                                                                       | Higher Cost<br>Higher value, larger size.                                                                                                                                                                 |  |  |  |  |  |  |  |  |  |

| Freewheeling Diode       | Lower Cost 75 ns ultrafast reverse recovery type (≤35 ns for ambient >70 °C).                                                                                  | <b>Higher Cost</b> 35 ns ultrafast recovery type required.                                                                                                                                                |  |  |  |  |  |  |  |  |  |

| LinkSwitch-TNZ           | Potentially Higher IC Cost May require larger device to deliver required output current – depends on required output current.                                  | Potentially Lowest IC Cost May allow smaller device to deliver required output current: depends on required output current.                                                                               |  |  |  |  |  |  |  |  |  |

| Efficiency               | Higher Efficiency Lower switching losses.                                                                                                                      | Lower Efficiency<br>Higher switching losses.                                                                                                                                                              |  |  |  |  |  |  |  |  |  |

| Overall                  | Typically lower cost but reduced output power.                                                                                                                 | Typically higher cost but increased output power.                                                                                                                                                         |  |  |  |  |  |  |  |  |  |

Table 7. Comparison of Mostly Discontinuous Conduction (MDCM) and Continuous Conduction (CCM) Modes of Operation.

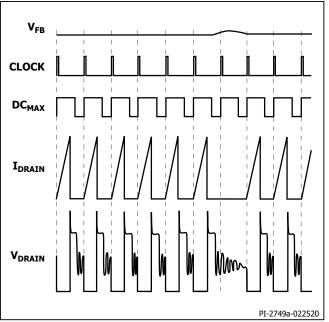

#### **ON/OFF Operation with Current Limit State Machine**

LNK33x7 has a special operating mode in which the current limit has multiple states depending on the output load. It has an advantage of generating less audible noise across varying load.

The internal clock of the LNK33x7 runs all the time. At the beginning of each clock cycle, it samples the FEEDBACK pin to decide whether or not to implement a switch cycle, and based on the sequence of samples over multiple cycles, it determines the appropriate current limit. At high loads, the state machine sets the current limit to its highest value. At lighter loads, the state machine reduces the current limit to reduced values.

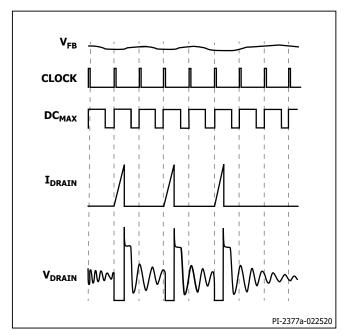

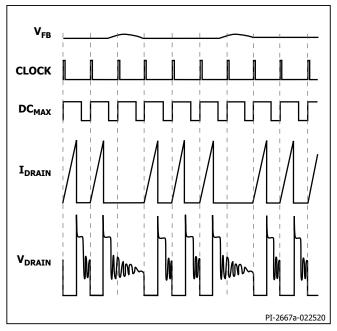

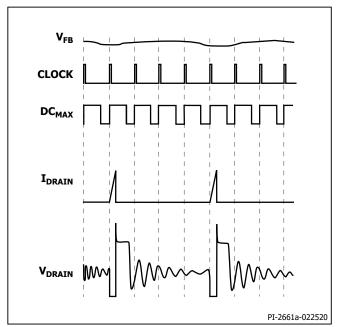

Figure 2. Operation at Near Maximum Loading (Flyback).

Figure 4. Operation at Medium Loading (Flyback).

At near maximum load, LNK33x7 will conduct during nearly all of its clock cycles (Figure 2). At slightly lower load, it will "skip" additional cycles in order to maintain voltage regulation at the power supply output (Figure 3). At medium loads, cycles will be skipped and the current limit will be reduced (Figure 4). At very light loads, the current limit will be needed to reduced even further (Figure 5). Only a small percentage of cycles will be needed to occur to satisfy the power consumption of the power supply.

The response time of the ON/OFF control scheme is very fast compared to PWM control. This provides accurate regulation and excellent transient response.

Figure 3. Operation at Moderately Heavy Loading (Flyback).

Figure 5. Operation at Very Light Load (Flyback).

#### **Step-by-Step Design Procedure**

## Enter Application Variables VAC $_{\rm MIN}$ , VAC $_{\rm MAX}$ , ${\bf f}_{\rm L}$ , V $_{\rm o}$ , I $_{\rm o}$ , ${\bf q}$ , C $_{\rm IN}$

|    | ACDC_LinkSwitchTNZ_Buck_052621;<br>Rev.1.0; Copyright Power Integrations |       |      |           |      |                                                                                    |

|----|--------------------------------------------------------------------------|-------|------|-----------|------|------------------------------------------------------------------------------------|

| 1  | 2021                                                                     | INPUT | INFO | OUTPUT    | UNIT | ACDC LinkSwitch™-TNZ Buck                                                          |

| 2  | ENTER APPLICATION VARIABLES                                              |       |      |           |      | Design Title                                                                       |

| 3  | LINE VOLTAGE RANGE                                                       |       |      | Universal |      | AC line voltage range                                                              |

| 4  | VACMIN                                                                   |       |      | 85.00     | V    | Minimum AC line voltage                                                            |

| 5  | VACMAX                                                                   |       |      | 265.00    | V    | Maximum AC line voltage                                                            |

| 6  | fL                                                                       |       |      | 60.00     | Hz   | AC mains frequency                                                                 |

|    |                                                                          |       |      |           |      | Line rectification type: select "F" if full wave rectification or "H" if half wave |

| 7  | LINE RECTIFICATION TYPE                                                  | F     |      | F         |      | rectification                                                                      |

| 8  | VOUT                                                                     | 12.00 |      | 12.00     | V    | Output voltage                                                                     |

| 9  | IOUT                                                                     | 0.500 |      | 0.500     | Α    | Average output current                                                             |

| 10 | EFFICIENCY_ESTIMATED                                                     |       |      | 0.80      |      | Efficiency estimate at output terminals                                            |

| 11 | EFFICIENCY_CALCULATED                                                    |       |      | 0.78      |      | Calculated efficiency based on real components and operating point                 |

| 12 | POUT                                                                     |       |      | 6.00      | W    | Continuous output power                                                            |

| 13 | CIN                                                                      |       |      | 15.00     | ъ    | Input capacitor                                                                    |

| 14 | VMIN                                                                     |       |      | 91.0      | V    | Valley voltage of the rectified minimum AC line voltage                            |

| 15 | VMAX                                                                     |       |      | 374.8     | V    | Peak voltage of the maximum AC line voltage                                        |

| 16 | INPUT STAGE RESISTANCE                                                   |       |      | 10        | Ohms | Input stage resistance in ohms (includes thermistor, filtering components, etc)    |

| 17 | PLOSS_INPUTSTAGE                                                         |       |      | 0.068     | W    | Maximum input stage loss                                                           |

Table 8. Application Variable Section of LinkSwitch-TNZ Design Spreadsheet.

#### **Input Voltage**

Determine the input voltage range from Table 9.

| Nominal Input Voltage (VAC) | VAC | VAC <sub>MAX</sub> |

|-----------------------------|-----|--------------------|

| 100/115                     | 85  | 132                |

| 230                         | 195 | 265                |

| Universal                   | 85  | 265                |

Table 9. Standard Worldwide Input Line Voltage Ranges.

#### Line Frequency, fL

50 Hz for universal or single 100 VAC, 60 Hz for single 115 VAC input. 50 Hz for single 230 VAC input. For most applications this gives adequate overall design margin. For absolute worst-case or based on the product specification, reduce these numbers by 6% (47 Hz or 56 Hz).

#### Nominal Output Voltage, V<sub>OUT</sub> (V)

Enter the nominal output voltage of the main output during the continuous load condition. Generally the main output is the output from which feedback is derived.

#### Output Current, $I_{OUT}$ (A)

Enter the output current of the power supply. If the power supply is a multiple output power supply, enter the sum total equivalent current of all the outputs, the sum total power divides the main output voltage.

In multiple output designs, the output power of the main output (typically the output from which feedback is taken) should be increased such that the maximum continuous output power as applicable, matches the sum of the output power from all the outputs in the design. The individual output voltages and currents should then be entered at the bottom of the spreadsheet.

#### Power Supply Efficiency, $\eta$

Enter the estimated efficiency of the complete power supply measured at the output terminals under peak load conditions and worst-case line (generally lowest input voltage). Start with a value of 0.7 for a 12 V output, 0.55 for a 5 V output if no better reference data is available, typical for a design where the majority of the output power is drawn from an output voltage of 12 V or greater. Once a prototype has been constructed then measured efficiency should be entered.

### Total Input Capacitance, $C_{IN}$ ( $\mu F$ )

Enter total input capacitance using Table 10 for guidance. The capacitance is used to calculate the minimum and maximum DC voltage across the bulk capacitor and should be selected to keep the minimum DC input voltage,  $V_{\mbox{\scriptsize MIN}} > 70 \mbox{ V}$ .

|                           | Total Input Capacitance per<br>Watt Output Power μF/W |                            |  |  |  |  |

|---------------------------|-------------------------------------------------------|----------------------------|--|--|--|--|

| AC Input Voltage<br>(VAC) | Full-Wave<br>Rectification                            | Half-Wave<br>Rectification |  |  |  |  |

| 100/115                   | 2                                                     | 4-5                        |  |  |  |  |

| 230                       | 1                                                     | 1-2                        |  |  |  |  |

| 85-265                    | 2                                                     | 4-5                        |  |  |  |  |

Table 10. Suggested Total Input Capacitance Values for Different Input Voltage Ranges.

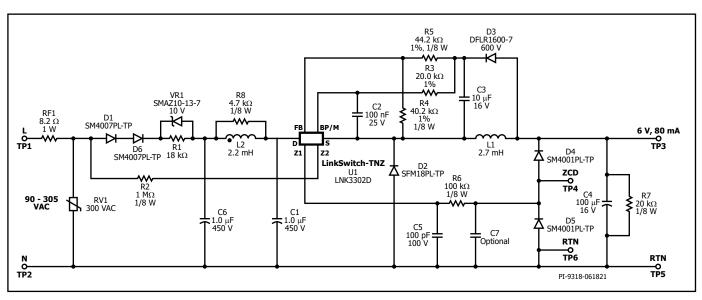

#### Step 2 – Determine AC Input Stage

The input stage comprises fusible resistor(s), input rectification diodes and line filter network. Flameproof fusible resistors are recommended and depending on the differential line input surge requirements, a wire-wound type may be required. The fusible resistor(s) provides fuse safety, inrush current limiting and differential mode noise attenuation. Table 12 shows the recommended input stage based on output power for a universal input design while Table 10 shows how to adjust the input capacitance for other input voltage ranges.

## Step 3 – Determine Minimum and Maximum DC Input Voltages $V_{\rm MIN}$ and $V_{\rm MAX}$ Based on AC Input Voltage

Calculate V<sub>MAX</sub> as:

$$V_{\text{MAX}} = \sqrt{2} \times V_{\text{ACMAX}}$$

(1)

Assuming that the value of input fusible resistor is small, the voltage drop across it can be ignored.

Derive minimum input voltage V<sub>MIN</sub>

Half-wave rectifier:

$$V_{\scriptscriptstyle MIN} = \sqrt{\left(2 \times {V_{\scriptscriptstyle ACMIN}}^2\right) - \frac{2 \times P_o\left(\frac{1}{f_L} - t_C\right)}{\eta \times C_{\scriptscriptstyle IN(TOTAL)}}}$$

Bridge rectifier:

$$V_{MIN} = \sqrt{\left(2 \times V_{ACMIN}^{2}\right) - \frac{2 \times P_{O}\left(\frac{1}{2 \times f_{L}} - t_{C}\right)}{\eta \times C_{IN(TOTAL)}}}$$

(3)

If  $V_{_{MIN}}$  is  $\leq 70$  V then increase value of  $C_{_{IN(TOTAL)}}.\ T_{_{C}}$  is the rectifier diode conduction time.

#### Step 4 – Select LinkSwitch-TNZ Device Based on Output Current, Current Limit and X Capacitor Discharge

Decide on the operating mode – refer to Table 7.

For MDCM operation, the output current  $\rm I_{\rm O}$  should be less than or equal to half the value of the minimum current limit of the chosen device from the data sheet.

$$I_{LIMIT\_MIN} > 2 \times I_O$$

(4)

For CCM operation, the device should be chosen such that the output current  $\rm I_{o}$  is more than 50% but less than 80% of the minimum current limit  $\rm I_{l\, IMIT\, MIN}$ .

$$0.5 \times I_{LIMIT\_MIN} < I_O < 0.8 \times I_{LIMIT\_MIN}$$

(5)

(2) Please see the data sheet for LinkSwitch-TNZ current limit values.

A typical LinkSwitch-TNZ part can be programmed to operate in one of the two current limits. The "RED" or reduced current limit enables operation at a reduced current limit and is recommended when the part is to be used at a current level considerably lower than the rated output current. A "STD" or standard current limit will be selected in most applications to optimize on BP capacitor cost.

Use of a 0.1  $\mu\text{F}$  capacitor results in the standard current limit value. Use of a 1  $\mu\text{F}$  capacitor results in the current limit being reduced, allowing design with lower cost surface-mount buck chokes.

|    | ENTER LINKSWITCH™-TNZ |      |          |   |                                                              |

|----|-----------------------|------|----------|---|--------------------------------------------------------------|

| 21 | VARIABLES             |      |          |   |                                                              |

| 22 | OPERATION MODE        |      | MCM      |   | Mostly continuous mode of operation                          |

|    |                       |      |          |   | Choose 'RED' for reduced current limit or 'STD' for standard |

| 23 | CURRENT LIMIT MODE    | STD  | STD      |   | current limit                                                |

| 24 | XCAP REQUIRED         | YES  | YES      |   | Select whether an X-capacitor is required or not             |

| 25 | PACKAGE               |      | SO-8C    |   | Device package                                               |

| 26 | DEVICE SERIES         | AUTO | LNK3317  |   | Generic LinkSwitch™-TNZ device                               |

| 27 | DEVICE CODE           |      | LNK3317D |   | Required LinkSwitch™-TNZ device                              |

| 28 | ILIMITMIN             |      | 0.725    | Α | Minimum current limit of the device                          |

| 29 | ILIMITTYP             |      | 0.780    | Α | Typical current limit of the device                          |

| 30 | ILIMITMAX             |      | 0.835    | Α | Maximum current limit of the device                          |

Table 11. LinkSwitch-TNZ Variable Section of LinkSwitch-TNZ Design Spreadsheet.

| POUT         | ≤0.25 W                                                                                                                                                                                  | 0.25 - 1 W                                                                                                                                                | >1                                                                                                                                                                                                                                                                        | . <b>W</b>                                                                                                                                                                                                                                                             |  |  |  |  |  |  |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| 85 - 265 VAC | AC IN R <sub>F2</sub> D <sub>IN1</sub> D <sub>IN2</sub> C <sub>IN</sub> PI-3771a-112221                                                                                                  | R <sub>F1</sub> D <sub>IN1</sub> D <sub>IN2</sub> R <sub>F2</sub> + C <sub>IN1</sub> C <sub>IN2</sub> C <sub>IN1</sub> PI-3772a-112221                    | AC IN PI-3773a-112221                                                                                                                                                                                                                                                     | D <sub>IN1-4</sub> AC IN  C <sub>IN1</sub> C <sub>IN2</sub> PI-3774-121603                                                                                                                                                                                             |  |  |  |  |  |  |

| Input Stage  | $R_{F1}$ , $R_{F2}$ : 100-470 Ω,<br>0.5 W, Fusible<br>$C_{IN}$ : ≥2.2 μF, 400 V<br>$D_{IN1}$ , $D_{IN2}$ : 1N4007, 1 A,<br>1000 V                                                        | $R_{F1}$ : 8.2 Ω, 1 W Fusible $R_{F2}$ : 100 Ω, 0.5 W, Flameproof $C_{IN1}$ , $C_{IN2}$ : ≥3.3 μF, 400 V each $D_{IN1}$ , $D_{IN2}$ : 1N4007, 1 A, 1000 V | $\begin{array}{l} R_{F1} \colon 8.2 \ \Omega, \ 1 \ W \ Fusible \\ L_{IN} \colon 470 \ \mu H - 2.2 \ mH, \\ 0.05 \ A - 0.3 \ A \\ C_{IN1}, \ C_{IN2} \colon \ge 4 \ \mu F/W_{OUT} \ 400 \ V \\ each \\ D_{IN1}, \ D_{IN2} \colon 1N4007, \ 1 \ A, \ 1000 \ V \end{array}$ | $\begin{array}{l} R_{F_1} \colon 8.2 \ \Omega, \ 1 \ W \ Fusible \\ L_{IN} \colon 470 \ \mu H - 2.2 \ mH, \\ 0.05 \ A - 0.3 \ A \\ C_{IN1}, C_{IN2} \colon \ge 2 \ \mu F/W_{OUT} \ 400 \ V \\ each \\ D_{IN1}, D_{IN2} \colon 1N4007, \ 1 \ A, \ 1000 \ V \end{array}$ |  |  |  |  |  |  |

| Comments     | *Optional for improved EMI and line surge performance. Remove for designs requiring no impedance in return rail.  **Increase value to meet required differential line surge performance. |                                                                                                                                                           |                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |

Table 12. Recommended AC Input Stages for Universal Input.

#### Step 5 - Select the Output Inductor

Choose any standard off-the-shelf inductor that meets the design requirements. As shown in the figure below, a "drum" or "dog bone" "I" core inductor is recommended with a single ferrite element due to its low cost and very low audible noise properties. However, the inductor should be selected as varnished type in order to get low audible noise.

Tables 4 and 5 provide inductor values and RMS current ratings for common output voltages and currents based on the calculations in the design spreadsheet. Select the next nearest higher voltage and/ or current above the required output specification. Alternatively, the PIXIs spreadsheet tool in the PI Expert software design suite or Appendix B can be used to calculate the exact inductor value (Eq. C13) and RMS current rating (Eq. C29). It is recommended that the value of inductor chosen should be closer to  $L_{\text{TYP}}$  rather than  $1.5 \times L_{\text{TYP}}$  due to lower DC resistance and higher RMS rating.

$$L_0 < 1.5 \times L_{TYP}$$

For LinkSwitch-TNZ designs, the mode of operation is not dependent on the inductor value. The mode of operation is a function of load current and current limit of the chosen device. The inductor value merely sets the average switching frequency. Table 14 shows a typical standard inductor manufacturer's data sheet. The value of off-the- shelf "drum core / dog bone / I core" inductors will drop up to 20% in value as the current increases. The constant  $K_{\rm L\_TOL}$  in equation (C14) and the design spreadsheet adjusts for both this drop and the initial inductance value tolerance. For example, if a 680  $\mu H_{\rm J}$  360 mA inductor is required, referring to Table 14, the tolerance is 10% and an estimated 9.5% for the reduction in inductance at the

operating current (approximately [0.36/0.38] x 10). Therefore the value of K  $_{\!\!\!\! L\ TOL}=0.195$  (19.5%).

Not all the energy stored in the inductor is delivered to the load due to losses after the LinkSwitch-TNZ device, the inductor (winding resistance and core losses), the freewheeling diode, feedback circuit, output capacitor loss and preload. This will limit the maximum power delivering capability and thus reduce the maximum output current. The minimum inductance must compensate for these losses in order to deliver specified full-load power. To compensate for this, a loss factor  $K_{\rm Loss}$  is used. This has a recommended value of between 50% and 66% of the total supply losses as given by equation 6. For example, a design with an overall efficiency  $(\eta)$  of 0.75 would have a  $K_{\rm Loss}$  value of between 0.875 and 0.833.

$$K_{LOSS} = 1 - \left(\frac{1-\eta}{2}\right) to 1 - \left(\frac{2(1-\eta)}{3}\right)$$

(6)

Figure 6. Example of Drum Core Inductor.

|    |                           | 1    | 1     | 1    | r                                                                 |

|----|---------------------------|------|-------|------|-------------------------------------------------------------------|

| 52 | BUCK INDUCTOR PARAMETERS  |      |       |      |                                                                   |

| 53 | INDUCTANCE_MIN            |      | 558   | uН   | Minimum design inductance required for current delivery           |

| 54 | INDUCTANCE_TYP            | AUTO | 620   | uН   | Typical design inductance required for current delivery           |

| 55 | INDUCTANCE_MAX            |      | 682   | uН   | Maximum design inductance required for current delivery           |

| 56 | TOLERANCE_INDUCTANCE      |      | 10    | %    | Tolerance of the design inductance                                |

| 57 | DC RESISTANCE OF INDUCTOR |      | 2.0   | ohms | DC resistance of the buck inductor                                |

|    |                           |      |       |      | Factor that accounts for "off-state" power loss to be supplied by |

| 58 | FACTOR_KLOSS              |      | 0.50  |      | inductor (usually between 50% to 66%)                             |

| 59 | IRMS_INDUCTOR             |      | 0.621 | Α    | Maximum inductor RMS current                                      |

| 60 | PLOSS_INDUCTOR            |      | 0.772 | W    | Maximum inductor losses                                           |

Table 13. Buck Inductor Parameters Section of LinkSwitch-TNZ Design Spreadsheet.

| ● SBC3 Series | Inductance and<br>Tolerance  | Current Rating<br>for 20 °C Rise | Current for 40 °C                           |                                    | Current Rating<br>for Value -10%         |  |  |

|---------------|------------------------------|----------------------------------|---------------------------------------------|------------------------------------|------------------------------------------|--|--|

| Model         | Inductance<br>L(µH) at 10 kH | Rdc $(\Omega)$ z) max.           | Rated Current (A) $\Delta T = 20 ^{\circ}C$ | Current $\Delta T = 40  ^{\circ}C$ | (Reference Value) (A) L change rate/-10% |  |  |

| 681-361       | 680±10%                      | 1.62                             | <b>→</b> 0.36                               | <b>₹</b> 0.50                      | 0.38 🚩                                   |  |  |

| 102-281       | 1000±10%                     | 2.37                             | 0.28                                        | 0.39                               | 0.31                                     |  |  |

| 152-251       | 1500±10%                     | 3.64                             | 0.25                                        | 0.35                               | 0.26                                     |  |  |

| 222-191       | 2200±10%                     | 5.62                             | 0.19                                        | 0.26                               | 0.21                                     |  |  |

| 332-151       | 3300±10%                     | 7.66                             | 0.15                                        | 0.21                               | 0.17                                     |  |  |

PI-3783-121521

Table 14. Example of Standard Inductor Data Sheet.

#### Step 6 - Select Freewheeling Diode

For MDCM operation at  $t_{_{AMB}} \le 70$  °C, select an ultrafast diode with  $t_{_{RR}} \le 75$  ns. At  $t_{_{AMB}} > 70$  °C,  $t_{_{RR}} \le 35$  ns. For CCM operation, select an ultrafast diode with  $t_{_{RR}} \le 35$  ns. Allowing 25% design margin for the freewheeling diode,

$$V_{PTV} = 1.25 \times V_{MAX} \tag{7}$$

The diode must be able to conduct the full load current. Thus:

$$I_{\scriptscriptstyle F} > 1.25 \times I_{\scriptscriptstyle O} \tag{8}$$

Table 3 lists common freewheeling diode choices.

#### Step 7 - Select Output Capacitor

The output capacitor should be chosen based on the output voltage ripple requirement. Typically the output voltage ripple is dominated by the capacitor ESR and can be estimated as:

$$ESR_{MAX} = \frac{V_{RIPPLE}}{I_{RIPPLE}} \tag{9}$$

Where  $V_{\text{RIPPLE}}$  is the maximum output ripple specification and  $I_{\text{RIPPLE}}$  is the LinkSwitch-TNZ output ripple current (Refer to equations C2 and C3 on appendix B).

The capacitor ESR value should be specified approximately at the switching frequency of 66 kHz. Capacitor values above 100  $\mu\text{F}$  are not recommended for non-resistive load as they can prevent the output voltage from reaching regulation during the 50 ms period prior to auto-restart. If more capacitance is required, then a soft-start capacitor should be added (see Tips for Design section). Select a voltage rating such that  $V_{\text{RATED}} \geq 1.25 \text{ x V}_{\text{O}}.$

#### Step 8 - Select the Feedback Resistors

The values of  $R_{FB}$  and  $R_{BIAS}$  are selected such that at the regulated output voltage, the voltage on the FEEDBACK pin ( $V_{FB}$ ) is 2 V. This voltage is specified for a FEEDBACK pin current ( $I_{FB}$ ) of 49  $\mu$ A.

Let the value of  $R_{\text{BIAS}}$  = 2.49  $k\Omega.$  This biases the feedback network at a current of

$$R_{FB} = \frac{V_O - V_{FB}}{\frac{V_{FB}}{R_{BIAS}} + I_{FB}} = \frac{(V_O - V_{FB}) \times R_{BIAS}}{V_{FB} + (I_{FB} \times R_{BIAS})}$$

(10)

#### Step 9 – Select the Feedback Diode and Capacitor

For the feedback capacitor, use a 10  $\mu$ F general purpose electrolytic capacitor with a voltage rating of  $\geq$  1.25 x  $V_0$ . For the feedback diode, use a glass-passivated 1N4005GP or DFLR1600-7 device with a voltage rating of  $\geq$  1.25 x  $V_{\text{\tiny MAX}}$ .

#### Step 10 – Select the External Biased Resistor for BYPASS Pin

The external BYPASS pin resistor  $R_{\rm BP}$  reduces the no-load input power for output voltage >  $V_{\rm RP/SHINNT}$ .

To achieve lowest no-load power consumption, the current fed into the BYPASS pin should be slightly higher than  $I_{\rm S1}$  on the data sheet. For best full-load efficiency and thermal performance, the current should be slightly higher than  $I_{\rm S2}$ .

The BYPASS pin current should not exceed 16 mA ( $I_{\rm BP(MAX)}$ ) at the maximum output voltage (normally when the output voltage is at no-load condition).

#### Step 11 - Select Preload Resistor

In high-side, direct feedback designs where the minimum load is < 3 mA, a preload resistor is required to maintain output regulation. This ensures sufficient inductor energy to pull the inductor side of the feedback capacitor  $C_{\rm FB}$  to input return via  $D_{\rm FB}$ . The value of  $R_{\rm PL}$  should be selected to give a minimum output load of 3 mA.

In designs with an optocoupler, a Zener diode or reference bias current provides a 1 mA to 2 mA minimum load, preventing "pulse bunching" and increased output ripple at zero load.

#### Step 12 – Select X Cap Discharge Components

If X cap discharge is required (PIXLS line 24), enter the X cap value on line 88. By default, the software calculates the discharge resistors  $\rm R_{\rm Z1}$  and  $\rm R_{\rm Z2}$  to ensure that the X cap discharges to 60 V after AC input disconnection in less than 1 second. Change the value of  $\rm R_{\rm Z1}$  to change the discharge time.

| 87 | X-CAPACITOR DISCHARGE COMPONENTS |       |       |       |                                                                                                     |

|----|----------------------------------|-------|-------|-------|-----------------------------------------------------------------------------------------------------|

| 88 | XCAP                             | 220.0 | 220.0 | ) nF  | X-capacitor in the input                                                                            |

| 89 | TOLERANCE_RZ                     | 0.05  | 5%    |       | Tolerance of the X-capacitor discharge resistors                                                    |

| 90 | RZ1                              | 1.00  | 1.00  | MOhms | X-capacitor discharge resistor connected from the input line to Z1 pin of LinkSwitch™-TNZ device    |

| 91 | RZ2                              |       | 1.00  | MOhms | X-capacitor discharge resistor connected from the input neutral to Z2 pin of LinkSwitch™-TNZ device |

| 92 | t XCAP DISCHARGE                 |       | 0.846 | 6 sec | Actual time (worst-case) to discharge the X-capacitor to 60 V after AC input disconnection          |

Table 15.F X Capacitor Discharge Section of LinkSwitch-TNZ Design Spreadsheet.

#### Step 13 – Select ZCD Configuration

### High-Side Buck, Half-Wave Rectification, ZCD Using Zener Diode

\* Xcap used on LNK-331x parts only

Figure 7. High-side Buck, Half-Wave Rectification, ZCD Using Zener Diode Schematic.

The basic implementation of the ZCD circuit is shown on Figure 7. This configuration is applicable to a high-side buck topology with half-wave input rectification in which the Neutral acts as the ground reference for the power supply.

While the AC input voltage is in positive (L > N) phase, the Z1/Z2 supply current of 22  $\mu$ A flows through VR1, anode to cathode. The voltage at the microcontroller ( $\mu$ C) input is therefore set to the VR1 Zener voltage ( $V_{7c}$ ).

During the next half-cycle (N > L), the Z1/Z2 supply current flows through VR1 in the opposite direction, cathode to anode. The  $\mu$ C zero cross input voltage is clamped to one diode drop below ground (-VF of VR1).

In non-X capacitor application, resistors  $R_{z_1}$  and  $R_{z_2}$  serve two purposes. First, they act as Safety protection in case Z1 and Z2 are shorted (see section about Safety). Second, the resistors help mitigate EMI noise. Since the Source pin is floating, switching noise are coupled to both the input and output.  $R_{z_1}$  reduces the magnitude of the switching noise currents. A value of between 500  $k\Omega$  and 1  $M\Omega$  is recommended for  $R_{z_1}$  and  $R_{z_2}$  for EMI mitigation. A smaller value is possible as long as EMI is ok and as long as the current does not exceed the Z1/Z2 rating. Higher values might improve EMI further. However, they might cause more delay on the ZCD signal.

The passive filter network CF1, CF2, and RF1 decouples switching noise from the ZCD signal. Values must be chosen to ensure no switching noise is coupled while keeping the delay to a minimum. The recommended values are the following: CF1 = 100 pF, RF1 = 100 k $\Omega$ , CF2 = 100 pF.

VR1 clamps the ZCD signal to a level that is below the pin voltage specifications of the microcontroller.

#### High-Side Buck, Half-Wave Rectification ZCD with 2 Diodes

Figure 8. High-side Buck, Half-Wave Rectification, ZCD With Two Diodes Schematic.

The next configuration replaces the Zener with two diodes. The component selection is similar to previous configuration except the Zener replaced with two diodes. With this option, the ZCD logic high signal is more controlled because it is clamped to VCC + a diode drop. It also offers less delay because the Zener typically has higher capacitance compared to ordinary diode.

On the other hand, this configuration is not compatible with X capacitor discharge. To do so, replace the diode  $D_{\text{\tiny ZCD1}}$  with a Zener.

#### **High-Side Buck, Half-Wave Rectification ZCD With MOSFET**

Figure 9. High-Side Buck, Half-wave Rectification, ZCD with MOSFET.

This configuration adds a MOSFET to the basic schematic on Figure 7. Here, the Zener diode VR1 clamps the gate voltage to less than the rating of MOSFT Q1. The recommended value is between 4.7 V and 10 V. The Drain of Q1 is then connected to the digital input of the microcontroller. The resistor  $R_{\rm PU}$  is the pullup to the VCC.

This option provides sharper rising-edge and falling-edge ZCD signal. Also, the signal is limited to VCC instead of VCC + diode drop.  $R_{\text{PU}}$  can be removed if the input of the MCU is programmed to have an internal pull-up. A stronger pull-up is required to get faster slew rate.

#### High-Side Buck, Full-Wave Rectification ZCD With MOSFET

Figure 10. High-side Buck, Full-Wave Rectification, ZCD With MOSFET Schematic.

Half-wave rectification is the ideal configuration for ZCD because the current flows in either phase of the AC line. However, higher power applications may require full-wave rectification in order to minimize the value and size of the bulk capacitor. The recommended ZCD schematic is shown in Figure 10. It is similar to figure 9 except for the required pull-down resistor  $R_{\mbox{\tiny PD}}$ . This resistor is to ensure Q1 can be turned-OFF properly and prevent any leakage current from falsely turning it ON.

One limitation of this circuit is the sensitivity to probing that can disrupt the ZCD signal. See Tips for Design section for recommendations.

#### **High-Side Buck-Boost, Half-Wave Rectification ZCD**

Figure 11. High-side Buck-Boost, Half-Wave Rectification, ZCD Schematic.

Figure 11 shows the typical implementation of ZCD in buck-boost converter. The circuit is also X cap discharge capable.

During the positive half-cycle, the Z1/Z2 current forward-biases VR1. The gate voltage ( $V_{GS}$ ) of Q1 is equal to  $V_{O} + V_{F(VR1)}$ . For a nominal 5 V output, this gives a  $V_{GS}$  of 5.5 V, allowing Q1 to be a low cost logic level device. The 2N7000 for example has a maximum gate threshold of 3 V. Applying 5.5 V will fully enhance the device, pulling down the zero cross input of  $\mu C$ .

During the next half-cycle, the Z1/Z2 current flows through VR1 in the opposite direction, cathode to anode. Therefore the  $V_{_{\rm GS}}$  of Q1 is equal to  $V_{_{\rm O}}-V_{_{\rm VR1}}.$  For a nominal 5 V output and 6.8 V Zener, the gate is therefore at -1.8 V, turning off Q1. The value of VR1 should be selected such that  $V_{_{\rm O}}-V_{_{\rm VR1}}\leq V_{_{\rm GS(TH)}}.$  The 2N7000 has a maximum  $V_{_{\rm GS(TH)}}$  value of 0.8 V and a maximum  $V_{_{\rm GS}(TH)}$  voltage of ±20 V.

No gate voltage clamping is required for  $\rm V_{\rm o}$  < 18 V. Above this, the voltage can be limited with a clamp Zener from gate to source or a resistor divider.

#### **Tips for Designs**

#### **Start-Up With Non-Resistive Loads**

If the total system capacitance is greater than 100  $\mu F$  or the output voltage is >12 V, then during start-up the output may fail to reach regulation within 50 ms which can trigger auto-restart protection feature. This may also be true when the load is not resistive, for example, the output is supplying a motor or fan. To increase the start-up time, a soft-start capacitor can be added across the feedback resistor as shown in Figure 12. The value of this soft-start capacitor is typically in the range of 0.47  $\mu F$  to 47  $\mu F$  with a voltage rating of 1.25 x  $V_{\rm o}$ . Addition of this capacitor can lead to instability in some designs that resembles bunching of switching cycles hence this recommendation should be carefully verified by measuring the output ripple under different operating conditions.

Figure 12. High-side Buck-Boost, Half-Wave Rectification ZCD Schematic.

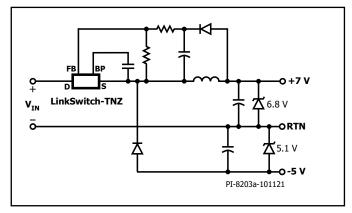

#### **Generating Negative and Positive Outputs**

In appliance applications, there is often a requirement to generate both an AC line-referenced positive and negative output. This can be accomplished using the circuit in Figure 13. The two Zener diodes have voltage rating close to the required output voltage for each rail and ensure that regulation is maintained when one rail is lightly and the other heavily loaded. The LinkSwitch-TNZ circuit is designed as if

it were a single output voltage with an output current equal to the sum of both outputs. The magnitude sum of the output voltages in this example is 12 V.

Figure 13. Example Schematic Showing Placement of Soft-Start Capacitor.

#### **Thermal Environment**

To ensure good thermal performance, the SOURCE pin temperature should be maintained below 110 °C by providing adequate heat sinking. For applications with high ambient temperature (>50 °C), it is recommended to build and test the power supply at the maximum operating ambient temperature and ensure that there is adequate thermal margin. The maximum output current specified in the data sheet is based on specific operating conditions and may need to be thermally derated. Also, it is recommended to use ultrafast ( $\leq$ 35 ns) low reverse recovery diodes at higher operating temperatures (>70 °C). If the device temperature exceeds 85 °C with ambient temperature of 25 °C, it is recommended the next bigger device in the family should be selected for the application.

A battery powered thermocouple meter is recommended to make measurements when the SOURCE pins are a switching node. Alternatively, the ambient temperature may be raised to indicate margin to thermal shutdown.

#### **Design for Lowest Input Standby Current**

In applications that require very low input leakage current during no-load or standby conditions (e.g., 2-wire smart switch), the following can be done to optimize the system for lowest input current:

Figure 14. Example Circuit - Generating Dual Output Voltages.

#### **R-Z Power Factor Circuit**

The proprietary R-Z circuit is an important component in many 2-wire (no neutral) applications where minimizing leakage current at standby operation is critical. The circuit is formed by connecting the parallel combination of resistor and zener in series with the input (Figure 14). The resistor shapes the input current to increase the power factor at standby. When the load demands more power, the resistor itself will limit the current. This is where the Zener diode comes in. It provides a path for the current to pass through when the load demands it. At standby, it is designed to be disabled. The recommended value for the Zener is between 10 V and 20 V. Higher value may increase the effective of the power factor and reduce the input current further. However, it also limits the bulk capacitor voltage. Also, higher values would dissipate more power during line surge. Hence, a 1 W rating or higher is recommended depending on the surge requirements.

Once the Zener voltage is selected, the resistor is then tuned such that the voltage across the resistor is below the Zener voltage to ensure that the Zener is disabled. This yields the lowest current that the R-Z circuit can provide.

When used in high-power design, the dissipation across the Zener diode could impact system efficiency. Hence, the circuit is recommended for low-power design or when demand for power only happens for a short duration (such as recloser, or powering a latching relay).

#### **Increase Feedback Resistors Resistors Value**

The default feedback resistors set the lower divider resistor to a value of 2.49 k $\Omega$ . The upper resistor is then calculated in order to set the FB voltage to 2 V. This method is enough to get <30 mW of standby power. However, if standby current is more critical, or if lower standby power is desired, then one way of doing it is to reduce the dissipation from the feedback resistors. Verify load transient response to ensure that the output voltage is still within specifications after changing the feedback resistors.

#### **Optimize BP Resistor**

For output voltage >5 V, adding an external current source to BP can reduce input current substantially. The resistor is computed to supply IS1 to BP.

#### **Optimize Pre-Load Resistor**

High-side configuration usually requires a pre-load to maintain regulation at no-load. However, many applications for LinkSwitch-TNZ usually have minimum load to power microcontroller and other auxiliary circuits. Hence, the pre-load resistor can be optimized based on minimum load instead of no-load.

## **Zero Crossing Detection Measurement for Bridge Rectifier System**

Buck and buck-boost designs with a ZCD circuit using bridge rectifier (Figure 10) may be sensitive to leakage current introduced by voltage probes or electronic loads.

The following are specific guidelines in probing and measuring the ZCD signal without compromising its signal integrity:

#### **Current Probe Method (Recommended Setup)**

While the ZCD signal being processed by the microcontroller is in terms of voltage, using a current probe to verify the signal prevents waveform distortion. Additional steps must be taken when using this technique:

- Avoid using an e-load. Use actual load or a resistive load instead

- Replace the pullup resistor RPU with lower resistance value in order to increase the current measurement resolution

- Place the current probe away from the IC or PCB to avoid switching noise coupling

- Use differential voltage probe to monitor the input voltage.

Figure 15. ZCD Signal using Current Measurement Set-up.

#### **Voltage Probe Method (Alternative Set-up)**

As an alternate set-up, the ZCD voltage can be measured using the following techniques:

- Connect input directly to AC mains line do not use an electronic AC source

- Make sure that the oscilloscope ground (earth) line is connected

- Use differential voltage probes

- · Use fixed resistor load instead of using e-load.

Figure 16. ZCD Signal using Voltage Measurement Set-up.

#### **Conducted EMI Considerations**

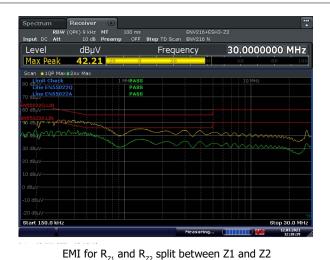

${f R_{z1}}+{f R_{z2}}$  Values On high-side buck or buck-boost configuration where the LinkSwitch-TNZ Source is floating, noise may be coupled to the line via ZCD circuit. This is not a big concern for applications with X capacitor. However, for low power design where X capacitor is

uncommon, EMI can be minimized by increasing the value of the series impedance  $(R_{71} + R_{72})$  with the input. The total impedance of 1  $M\Omega$  provides a balance between EMI and ZCD delay.

#### **Inductor Placement**

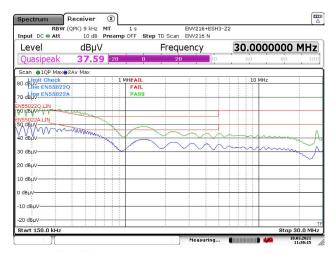

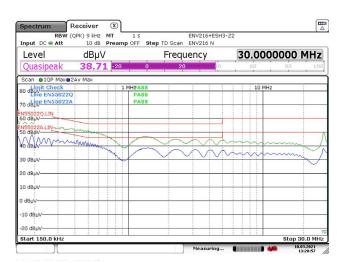

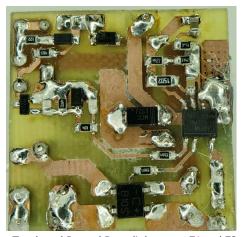

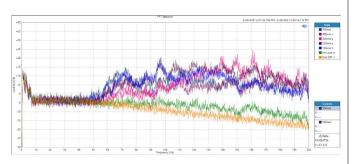

When using unshielded buck inductor, place it as far away from the AC input as possible. Comparison chart below shows how inductor placement can have significant EMI impact.

Buck inductor placed at the middle of the board closer to ac input

Buck inductor placed away from the ac input

Failed EMI when inductor placed at the middle of the board closer to ac input

Passed EMI when buck inductor placed at the middle of the board closer to ac input

Table 16. Inductor Placement Impact on EMI.

**AN-98 Application Note**

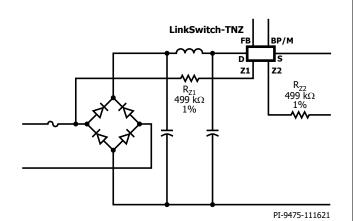

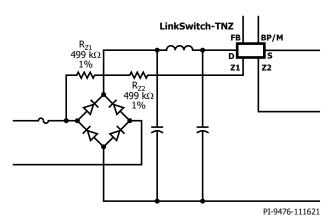

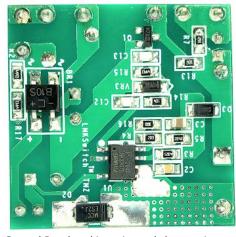

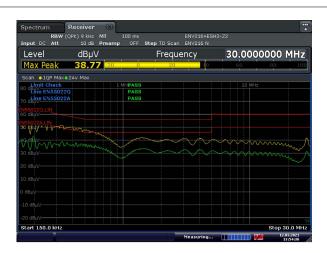

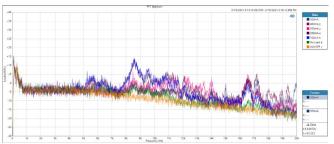

$R_{z1}$ ,  $R_{z2}$  Placement

Aside from optimizing the value of  $R_{z1}$  and  $R_{z2}$ , their PCB mounting location also affects EMI. To get best EMI performance, place  $R_{z1}$  resistor closer to the AC input. Some designs may also benefit by connecting  $R_{z1}$  and  $R_{z2}$  in series and placing them closer the AC input as shown in the example below.

$R_{71}$  and  $R_{72}$  split between Z1 and Z2 schematic

$R_{71}$  and  $R_{72}$  placed in series and closer to input

Test board  $R_{z_1}$  and  $R_{z_2}$  split between Z1 and Z2

$R_{z_1}$  and  $R_{z_2}$  placed in series and closer to input

Table 17. Inductor Placement Impact on EMI.

Lower EMI for R<sub>71</sub> and R<sub>72</sub> placed in series and closer to input

#### **Tips for Audible Noise Reduction**

- Use LNK3307D. It has a built-in current limit state machine that adjusts the current limit automatically based on load condition. At high loads, the state machine sets the current limit to its highest value. At lighter loads, the state machine sets the current limit to reduced values.

- Add hot melt glue around noise-inducing components like the power inductor.

- When using a "dog bone" or barrel type inductor, change orientation from vertical to horizontal mounting.

- Keep the inductor away from other large components.

#### **Inductor Type and Mounting Orientation**

Shielded Buck inductor mounted vertically

Dog-bone Buck inductor mounted horizontally

SMD Shielded Inductor in vertical mounting generates more vibration in PCB Audible Noise < 25dBSPL

Dog Bone Type Inductor mounted horizontally Audible Noise < 10dBSPL

Table 18. Inductor Type and Orientation Impact on Audible Noise.

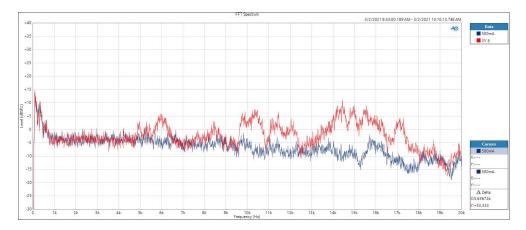

#### Type of Adhesive/Glue to Reduce Component Vibration

Table 19 shows the audible noise performance between two type of glue – hot melt glue (SDL4062-ND) and Devcon Epoxy. The former is more elastic and acts like a cushion to minimize inductor vibration while the latter is hard and brittle which may worsen PCB vibration especially at full load.

Hot Melt Glue (SDL4062-ND)

Devcon Epoxy

Audible noise comparsion between two types of adhesives

Table 19. Glue Type and Impact on Audible Noise.

#### Special Consideration for LNK33x7D

LNK3307D and LNK3317D are the only devices in the LinkSwitch-TNZ product family that have current limit state machine (see Figures 2 to 5). As the output load is changed, the current limit also transitions to a different state. In some cases, pulse grouping may occur if the current limit is stuck from going back and forth one state change to

another. This condition is more prone to happen at high line input, and with heavier or more CCM load.

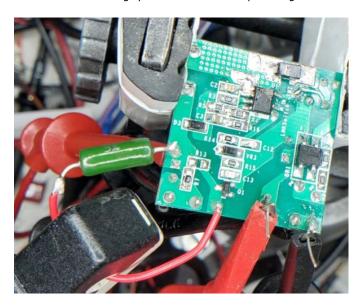

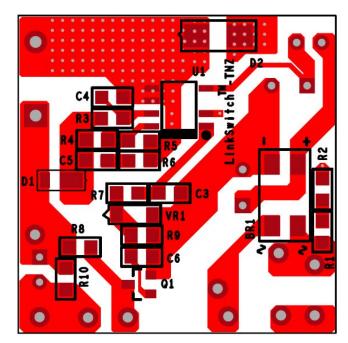

Figure 17 shows the recommended circuit when using LNK33x7D in high-side buck or buck-boost applications. Resistor R6 is added and connected in series with feedback capacitor C5.

Figure 17. Glue Type and Impact on Audible Noise.

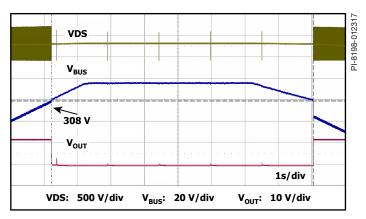

With R6 shorted, the waveforms looked normal at 300 mA load current (Figure 18). At 400 mA load (Figure 19), huge oscillation can be seen on the output voltage due to pulse grouping of the Drain current. This condition not only causes huge output voltage ripple but it can also result to higher audible noise.

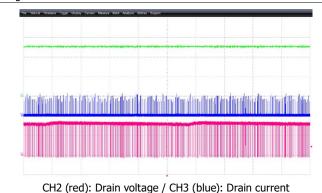

CH4 (green): Output voltage

Figure 18. 230 VAC, 50 Hz, 300 mA load, R6 shorted.

CH2 (red): Drain voltage / CH3 (blue): Drain current CH4 (green): Output voltage

Figure 19. 230 VAC, 50 Hz, 400 mA load, R6 shorted.

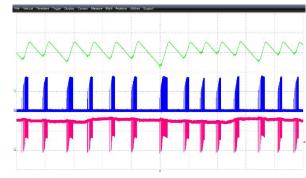

With R6 connected, Figures 21 and 22 show that the oscillation is gone.

CH4 (green): Output voltage

CH2 (red): Drain voltage / CH3 (blue): Drain current CH4 (green): Output voltage

Figure 21. 230 VAC, 50 Hz, 400 mA load, R6 = 30  $\Omega$ .

Figure 20. 230 VAC, 50 Hz, 300 mA load, R6 = 30  $\Omega$ .

The drawback with this circuit is the slightly worse load regulation. Thus, choose a value between 4.7  $\Omega$  and 30  $\Omega$  to balance between regulation and output ripple.

#### **Recommended Layout Considerations**

### Managing Thermals for High Power (High Current) Designs

- Use double-sided PCB with 2 oz copper

- Maximize copper area connected to SOURCE pins

- Provide enough copper heat sink on freewheeling diode.

#### **Minimizing Noise**

Minimize the loop formed between LinkSwitch-TNZ DRAIN and SOURCE pins, freewheeling diode, and input capacitor traces carrying high current should be as short and thick as possible

- Keep output inductor away from the AC input whenever possible

- Controlling the start and end orientation of the output inductor when mounting on the board, especially for drum-core type, may help reduce EMI

- Place RZ1 and RZ2 resistors closer to AC input.

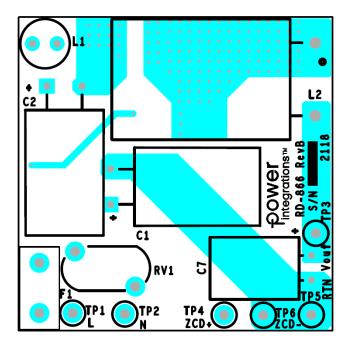

Figure 22. Recommended Printed Circuit Layout for LinkSwitch-TNZ using D Package.

#### **Design for Safety Compliance**

#### **Z1/Z2** Creepage and Clearance

Based on UL/IEC 60950 safety standard, functional insulation can be met by satisfying any of these conditions:

- 1. Creepage and clearance requirements for functional insulation.

- 2. Withstand electric strength tests for functional insulation.

- Short-circuited and there is no overheating of any material creating a risk of fire, no emission of molten material, no opening of PCB trace, and the temperature is within limits.

Z1 and Z2 pins functional safety compliance falls under condition 3 - i.e., even if the pins are shorted, there will be no risk of Safety violation as long as the external components (resistors, capacitors) are rated properly.

#### **RZ1 and RZ2 Device Rating**

When used as an X cap discharge, the voltage rating of the resistors should be able to handle the maximum input operating voltage. If used for ZCD only, then the resistors should not cause Safety failure when Z1 and Z2 pins are short-circuited.

#### **Design for Surge Withstand**

Power supplies are required to have capability of withstanding surge voltages which typically are a result of events such as lightning strikes. It is expected that such events do not lead to failure of any components or loss of functionality. Standards such as IEC61000-4-5 defines surge voltage and current waveforms as well as source impedance, which emulate typical worst case transients for testing of protection mechanisms for line connected power circuits and data line connected equipment.

Components of the fusible resistor, EMI filter and the capacitors used in the power supply input stage, help in limiting the voltage and current stress that the components of the power supply are subjected to during these events.

MOVs will often be required to be added at the input of the power supply if the surge level is high (DM surge >1 kV). These MOVs are placed after the input fuse and help in clamping the voltage at the input of the power supply when a surge event occurs.

Use the following checklist to ensure that the design is compliant to the applicable requirements:

- Define the target market for LinkSwitch-TNZ converter.

- Determine the equipment class to determine common-mode (CM) and differential-mode (DM) surge levels.

- If DM surge >1000 V, then you will likely need to include an MOV across the AC line at the front-end of the EMI filter

- Select a MOV for North America 115 VAC or universal input with adequate stand-off voltage during normal operation as well as adequate rated surge current and energy capacity.